LABORATORIO # 6

PROGRAMACIÓN DEL MICROPROCESADOR 8085

Objetivos

Realizar la sección de inicialización del programa Monitor.

Programar las secciones de retardo y despliegue del programa monitor.

Realizar la Programación para manejo del teclado hexadecimal y de teclas de función.

Utilizar los recursos del programa Monitor para programación de programas de aplicación.

Parte 1

Lea detenidamente el marco teórico de la LECCIÓN 9 PROGRAMA MONITOR Y LECCIÓN 10 PROGRAMA 1 y realice la experiencia indicada en la sección de PROCEDIMIENTO.

Parte 2

Lea detenidamente el marco teórico de la LECCIÓN 11 PROGRAMA 2 y realice la experiencia indicada en la sección de PROCEDIMIENTO.

Parte 3

Lea detenidamente el marco teórico de la LECCIÓN 12 PROGRAMA 3 y realice la experiencia indicada en la sección de PROCEDIMIENTO.

Parte 4

Lea detenidamente el marco teórico de la LECCIÓN 13 PROGRAMA 4 y realice la experiencia indicada en la sección de PROCEDIMIENTO.

Parte 5

Lea detenidamente el marco teórico de la LECCIÓN 14 PROGRAMA 5 y realice la experiencia indicada en la sección de PROCEDIMIENTO.

LECCIÓN 7

DESCRIPCIÓN FUNCIONAL DEL 8085-A

QUE ES EL 8085-A

El 8085-A es un microprocesador de 8 bits de propósito general que es muy costo-efectivo

en pequeños sistemas debido a su bajo requerimiento de hardware adicional. Al mismo

tiempo es capaz de acceder hasta 64K bytes de memoria y tiene líneas de estado para

controlar grandes sistemas.

Que hay en el 8085-A

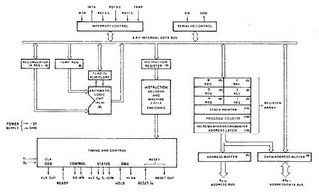

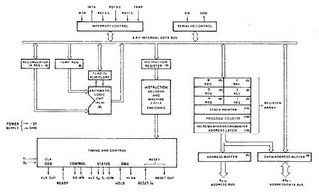

En el microprocesador 8085-A están contenidas las funciones de la generación de reloj, el

control del sistema de bus, y selección de la prioridad de interrupciones, en adición a la

ejecución del conjunto de instrucciones. (ver la figura 7-1) El 8085-A transfiere los datos

por un bus de tres estados bidireccional de 8 bits (AD0 – AD7) el que es multiplexado en

tiempo para transmitir también los ocho bits de orden inferior de la dirección. Ocho líneas

adicionales (A8 – A15), expanden la capacidad de direccionamiento de memoria a 16 bits,

permitiendo por lo tanto el acceso directo, por la CPU, a 64K bytes de memoria. La CPU

8085-A(unidad central de procesamiento) genera las señales de control que pueden ser

usadas para seleccionar los dispositivos externos apropiados para realizar las funciones de

LECTURA y ESCRITURA y también para seleccionar la memoria o los puertos I/O. El

8085-A puede direccionar hasta 256 dispositivos de I/O diferentes. Estas direcciones tienen

el mismo valor numérico (00H a FFH) que las primeras 256 posiciones de memoria; éstas se

distinguen por medio de la señal de salida IO/⎯M de la CPU. También se puede asignar

direcciones de memoria para seleccionar puertos de I/O (dispositivos de I/O por mapeo de

memoria).

Registros

El 8085-A como el 8080, esta provisto con registros internos de 8 y 16 bits. El 8085-A tiene

8 registros direccionables de 8 bits. Seis de los cuales pueden utilizarse como registros de 8

bits o como pares de registros de 16 bits. Los pares de registros son tratados como si fueran

registros individuales de 16 bits; el byte de orden superior del par de registros está

localizado en el primer registro y el byte de orden inferior se localiza en el segundo.

Adicionalmente a los pares de registros, el 8085-A contiene dos registros de 16 bits.

Figura 7-1 DIAGRAMA EN BLOQUES FUNCIONAL DE LA CPU DEL 8085-A

Los registros de la CPU del 8085-A están distinguidos como sigue:

El acumulador (Registro ACC o A) es el foco de todas las instrucciones de acumulador(tablas 8-1 y 8-2), las que incluyen las instrucciones aritméticas, lógicas, de carga y almacenamiento, y de I/O. Es un registro de solo 8 bits. (Sin embargo, ver Indicadores en esta lista).

El contador de programa (PC) siempre apunta a la posición de memoria de la siguiente instrucción a ser ejecutada. Contiene siempre una dirección de 16 bits.

Registros de propósito general BD, DE, y HL pueden ser usados como seis registros de 8 bits o como tres de 16 bits, la intercambiabilidad, depende de la instrucción que se está efectuando. El par HL funciona como puntero de datos para referencia de dirección de memoria ya sea como fuente o como destino en numerosas instrucciones. Un número menor de instrucciones pueden utilizar los pares BC y DE para direccionamiento indirecto.

El puntero de stack (SP) es un puntero de datos especial que apunta siempre al tope del stack (próxima dirección disponible del stack). Es un registro indivisible de 16 bits.

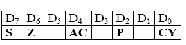

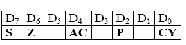

El registro de indicadores contiene 5 indicadores de 1 bit, cada uno de los cuales registra la información de estado del procesador y puede también controlar la operación del procesador. (Ver el siguiente párrafo)

Indicadores

Se muestran los 5 indicadores de la CPU del 8085-A:

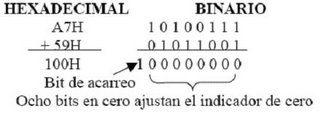

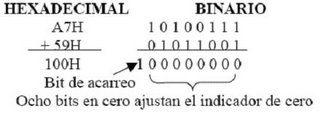

El indicador de acarreo (CY) es repuesto y ajustado por las operaciones aritméticas.

Su estado puede ser verificado directamente por el programa. Por ejemplo, la suma de dos números de un byte puede producir una respuesta que no cabe en un byte:

Una operación que da como resultado un rebasamiento del bit de orden superior en el

acumulador pone en 1 al indicador de acarreo. La operación de suma que no termina con

rebasamiento borra el indicador de acarreo. (Ver la lección 8 para más detalles.) El indicador de acarreo también actúa como indicador de llevo para las operaciones de resta.

El indicador de acarreo auxiliar (AC) indica rebasamiento del bit 3 del acumulador de la misma forma que el indicador de acarreo indica rebasamiento del bit 7. Este acarreo se utiliza por lo común en la aritmética BCD.

El indicador de signo es puesto con el valor del bit más significativo del acumulador

siguiendo la ejecución de las instrucciones aritméticas o lógicas. Estas instrucciones utilizan el bit 7 de los datos para representar el signo de los números contenidos en el acumulador.Esto permite la manipulación de los números en el rango desde –128 a +127.

El indicador de cero es puesto a 1 si el resultado generado por ciertas instrucciones es cero.El indicador de cero es borrado si el resultado no es cero. El resultado que tiene un acarreo pero que tiene la respuesta de cero en el acumulador pondrá ambos indicadores en 1, el de cero y el de acarreo. Por ejemplo:

El incremento o decremento de ciertos registros de la CPU con resultado de cero también pondrán en 1 el indicador de cero.

El indicador de paridad (P) es puesto a 1 si la paridad (número de bits en 1) del acumulador es par. Si es impar se borra.

Stack

El puntero de stack mantiene la dirección del último byte introducido en el stack. El puntero de stack puede ser inicializado para utilizar cualquier porción de la memoria de lectura/escritura como stack. El puntero de stack es decrementado cada vez que se introducen datos en el stack y se incrementa cada vez que los datos son recuperados del stack (el stack crece hacia abajo en términos de direcciones de memoria y el tope del stack es la dirección numérica más baja del stack que se utiliza actualmente. Note que el puntero de stack se incrementa o decrementa siempre en dos bytes ya que todas las operaciones de stack se aplican a los pares de registros.

Unidad aritmética lógica (ALU)

La ALU contiene el acumulador, el registro de estados, y algunos registros temporales que son inaccesibles para el programador. Las operaciones aritméticas, lógicas, y de rotación son efectuadas por la ALU. Los resultados de esas operaciones pueden ser depositadas en el acumulador, o pueden ser transferidas al bus de datos interno para su uso en algún otro lugar.

Registro y decodificador de instrucciones

Durante la búsqueda de una instrucción, el primer byte de una instrucción conteniendo el código de instrucción) es transferido desde el bus interno al registro de instrucciones de 8 bits. (Ver figura 7-1). El contenido del registro de instrucciones, está en su momento disponible para el decodificador de instrucciones. La salida del decodificador, está asociada con las señales de temporización, controlan los registros, la ALU, y los buffers de datos y direcciones. Las salidas del decodificador de instrucciones y el generador de reloj interno generan las señales de temporización de los estados y ciclos de máquina.

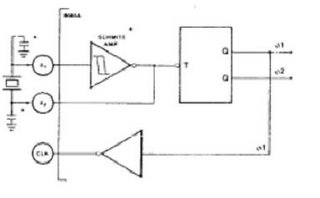

Generador interno de reloj

La CPU 8085-A incorpora un generador de reloj completo en la pastilla, así, solo requiere la adición de un cristal de cuarzo para establecer la temporización para su operación. (Sin embargo, en su lugar aceptará una señal de reloj externa en su entrada X.

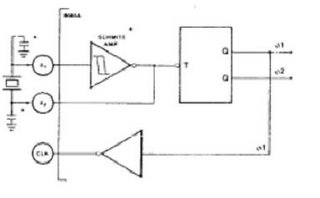

1)Un cristal adecuado para el 8085-A estandar debe ser resonante en paralelo en la frecuencia fundamental de 6.25 MHz o menos, dos veces la frecuencia de reloj interno deseada. El 8085-A-2 operará con un cristal de hasta 10MHz. Las funciones del generador interno de reloj se muestra en la figura 7-2. Como oscilador o como acondicionador de entrada, se utiliza un disparador de Schmitt , dependiendo de si se usa un cristal o una fuente externa.La circuitería de reloj genera dos señales de reloj interno no solapadas φ1 y φ2 (ver figura 7

2)φ1 y φ2 controlan la temporización interna del 8085-A y no están directamente

disponibles en el exterior de la pastilla. El pin de CLK externo es la versión almacenada invertida de φ1 . El CLK es la mitad de la frecuencia de la señal de entrada del cristal, y puede ser utilizada para la temporización de otros dispositivos del sistema.

• SE REQUIEREN CAPACITORE EXTERNOS SOLO PARA LAS FRECUENCIAS DE CRISTAL

Figura 7-2 LOGICA DE RELOJ DEL 8085-A

Si los requerimientos de frecuencia de reloj no son tan exigentes como para requerir un cristal, se puede utilizar un red RC. La red RC mostrada en la figura 10-3 da una

frecuencia aproximada de 3MHz.

Interrupciones

Las cinco entradas de interrupción por hardware provistas en el 8085-A son de tres tipos. INTR es enmascarable (se puede habilitar o deshabilitar por las instrucciones de software EI y DI), y provocan que la CPU busque una instrucción RST, externamente

colocada en el bus de datos, que vectoriza a una ramificación a cualquiera de ocho

posiciones fijas de memoria (direcciones de reinicio). (Ver figura 7.3).

Figura 7-3 UBICACIONES DE LAS RAMIFICACIONES RST HARDWARE Y SOFTWARE DEL 8085-A

El requerimiento de interrupción INTR también puede ser controlado por el controlador

de interrupciones programable 8259, que genera una instrucción CALL en lugar de RSTs, y puede así, realizar la operación de vectorización de la CPU a una subrutina

preprogramada, localizada en cualquier parte del mapeo de memoria de su sistema. Las

interrupciones de hardware RST 5.5, RST 6.5,y RST 7.5 son diferentes porque son

enmascarables mediante el uso de la instrucción SIM, la cual habilita o deshabilita éstas interrupciones poniendo a 1 o borrando los indicadores de máscara correspondientes, basados en los datos del acumulador. (Ver figura 7-4)

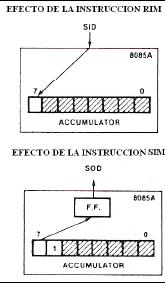

7-4 AJUSTE DE LA MASCARA DE INTERRUPCIONES UTILIZANDO LA INSTRUCCIÓN SIM

Usted puede leer el estado de la máscara de interrupciones previamente ajustada

ejecutando la instrucción RIM. Su ejecución carga al acumulador la siguiente

información : (Ver figura 7 – 5)

• Estado de la máscara de las actuales interrupciones para RST 5.5, 6.5, y el estado

hardware de la 7.5.

• El estado del indicador de habilitación de interrupciones (excepto que siguiendo

un TRAP, inmediatamente se carga el estado del indicador IE precedente a esa

interrupción)

• Las interrupciones RST 5.5, 6.5, y 7.5 pendientes.

Figura 7-5 LECTURA DE MASCARA DE INTERRUPCION – RIM

Las interrupciones RST 5.5, 6.5, y 7.5 son también sujetas ha ser habilitadas o

deshabilitadas por las instrucciones EI y DI, respectivamente. Las interrupciones INTR,

RST 5.5, y 6.5 son sensibles por nivel, significando que éstas entradas pueden ser

reconocidas por el procesador cuando se las mantiene en nivel alto. La RST 7.5 es

sensible por flanco, significando que un flip flop interno del 8085-A registra la

ocurrencia de una interrupción en el instante que aparece el flanco ascendente en la línea

de entrada RST 7.5. Esta entrada no requiere ser mantenida en nivel alto; el flip flop

permanecerá ajustado hasta que sea borrado por una de las siguientes tres posibles

acciones:

• El 8085-A responde a la interrupción, y envía una señal de borrado interno al flip

flop del RST 7.5 (Ver figura 7-6A).

• El 8085-A, después de responder la interrupción RST 7.5, recibe una señal

⎯R⎯E⎯S⎯E⎯T⎯ ⎯I⎯N desde una fuente externa; esto también activa el reset

interno.

• El 8085-A ejecuta la instrucción SIM, con el bit 4 del acumulador previamente

ajustado a 1. (Ver la figura 7-4).

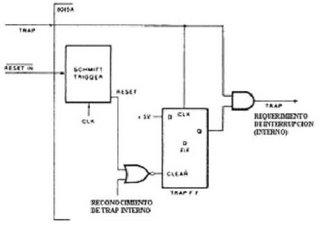

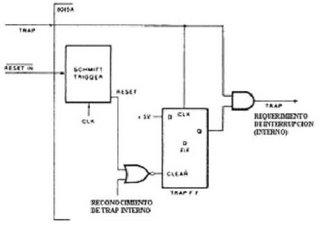

Figura 7-6A FLIP FLOP RST 7.5

Figura 7-6B ENTRADAS DE INTERRUPCION TRAP

El tercer tipo de hardware es TRAP. Esta entrada no ésta sujeta a ninguna máscara o

instrucción de habilitación/deshabilitación. La recepción de un flanco positivo en la

línea de entrada TRAP dispara la secuencia de interrupción por hardware del

microprocesador, pero el pulso debe ser mantenido en nivel alto hasta que sea

reconocido internamente (ver la figura 7-6B).

El muestreo de todas las interrupciones ocurre en el flanco descendente del CLK, un

ciclo después del final de la instrucción en la cual se activó la entrada de

interrupción. Para ser reconocida, como una interrupción válida debe ocurrir por lo

menos 160 ns antes del tiempo de muestreo en el 8085-A, o 150 ns en el 8085-A-2.

Esto significa que para garantizar ser reconocida, la RST 5.5 y RST 6.5 Y TRAP

necesitan ser mantenidas por lo menos 17 estados de reloj más 160 ns (150 para el

8085-A-2), asumiendo que la interrupción debe llegar justo algo tarde para ser

reconocida durante una instrucción particular, y que la siguiente instrucción podría

ser una CALL de 18 estados. Esta temporización asume que no se utilizan ciclos

WAIT o HOLD.

La manera en que la máscara de interrupciones es ajustada y leída se describe en la

lección 8 en la lista de instrucciones RIM (lectura de la máscara de interrupciones) y SIM (ajustar máscara de interrupciones).

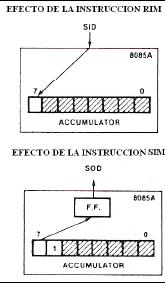

Entrada y Salida Serial

Los pines SID y SOD ayudan a minimizar la cantidad de pastillas en un sistema pequeño

proporcionando facilidad para interfazar a un puerto serial utilizando software par la temporización y codificación de los datos. Cada vez que se ejecuta una instrucción RIM, se lee el estado del pin SID al bit 7 del acumulador. Así, la instrucción RIM es de doble propósito. (Ver la lección 8). De forma similar, la instrucción SIM es utilizada para transferir el bit 7 del acumulador al pin de salida SOD por medio del flip flop interno, procurando que el bit 6 del acumulador este ajustado en 1. (Ver figura 7-7). La temporización de SID y SOD se describirá posteriormente. La instrucción SID también se puede usar como una entrada de prueba de propósito general y la SOD puede servir como una salida de control de un bit.

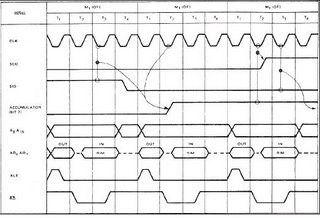

TEMPORIZACIÓN DE LOS CICLOS DE BUS MULTIPLEXADOS

La ejecución de cualquier programa del 8085-A consiste en una secuencia de operaciones de LECTURA y ESCRITURA, de las cuales cada una transfiere un byte de datos entre el 8085-A y una dirección particular de memoria o E/S. Estas operaciones de LECTURA y ESCRITURA son la única comunicación entre el procesador y los otros componentes, y son todo lo necesario para ejecutar cualquier instrucción de programa.

Cada operación de LECTURA o ESCRITURA del 8085-A es referida como un ciclo de

máquina. La ejecución de cada instrucción del 8085-A consta de una secuencia de uno a

cinco ciclos de máquina, y cada ciclo de máquina consta de un mínimo de tres a seis ciclos de reloj (también referidos como estados T). Considere el caso de la instrucción Almacenar Directamente el Acumulador (STA), mostrada en la figura 7-8.

La instrucción STA causa que el contenido del acumulador sea almacenado directamente en la dirección especificada en el segundo y tercer byte de la instrucción. Durante el primer ciclo de máquina (M1), la CPU pone el contenido del contador de programa (PC) en el bus de direcciones y realiza un ciclo de LECTURA DE MEMORIA, para leer desde la memoria el código de operación de la siguiente instrucción (STA). El ciclo de máquina M1 también es referido como el ciclo de BÚSQUEDA DE CODIGO DE OPERACIÓN, ya que éste busca el código de operación de la siguiente instrucción. En el cuarto ciclo de reloj (T4) de M1 la CPU interpreta los datos leídos y los reconoce como el código de operación de la instrucción STA. En éste punto la CPU sabe que debe hacer tres ciclos de máquina más (dos de LECTURA DE MEMORIA y una de ESCRITURA DE MEMORIA) para completar la instrucción.

Luego, el 8085A incrementa el contador de programa de manera tal que apunte al siguiente byte de la instrucción y realiza el ciclo de máquina (M2) de LECTURA DE MEMORIA de la dirección (PC + 1). La memoria accesada coloca los datos de dirección en el bus de datos de la CPU. El 8085-A almacena temporalmente este dato (el cual es el byte de orden inferior de la dirección directa) internamente en la CPU. El 8085-A nuevamente incrementa el contador de programa a la posición (PC + 2) y lee desde la memoria (M3) el siguiente byte de datos, el cual es el byte de orden superior de la dirección directa.

En este punto, el El 8085-A ha accesado los tres bytes de la instrucción STA, la cual ahora va ha ejecutar. La ejecución consiste en colocar los datos accesados en M2 y M3 al bus de direcciones, luego colocar el contenido del acumulador al bus de datos, y luego realizar el ciclo de máquina (M4) de ESCRITURA DE MEMORIA. Cuando finaliza M4 , la CPU conseguirá (M1) el primer byte de la siguiente instrucción y continuará.

Secuencia de transiciones de estado

Como muestra el ejemplo anterior, la ejecución de una instrucción consta de una serie de ciclos de máquina cuya naturaleza y secuencia está determinada por el código de operación accesado en el ciclo de máquina M1. Mientras que ninguna instrucción constará de más de cinco ciclos de máquina, cada ciclo de máquina será uno de los siete tipos de listados. Estos siete tipos de ciclos de máquina pueden ser diferenciados por el estado de tres líneas de estado (IO/⎯M, S0, y S1) y tres señales de control (⎯R⎯D, ⎯W⎯R, e ⎯I⎯N⎯T⎯A).

La mayoría de los ciclos de máquina constan de tres estados T, (ciclos de reloj) con la excepción del ciclo de BÚSQUEDA DE CODIGO DE OPERACIÓN, el cual, normalmente

tienen entre cuatro y seis estados T. El número de estados requerido para realizar cualquier instrucción depende de la instrucción que está ejecutando el ciclo de máquina particular dentro del ciclo de instrucción, y el número de estados de espera y contención (WAIT y HOLD) insertados en cada ciclo de máquina mediante el uso de las entradas READY y HOLD del 8085-A. El diagrama de transiciones de estadoilustra como procede el 8085-A en el curso de un ciclo de máquina. El estado de varios estados y señales de control, como también los buses del sistema, son mostrados en la figura 7-11 para cada uno de los diez posibles estados T a los que puede entrar el procesador.

BÚSQUEDA DEL CODIGO DE OPERACIÓN (OF):

El ciclo de máquina de búsqueda del código de operación es único por tener más de tres ciclos de reloj. Esto porque la CPU debe interpretar el código de operación accesado en los ciclos T1, T21 y T3 antes que pueda decidir que hacer después.

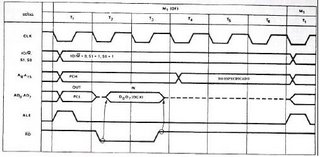

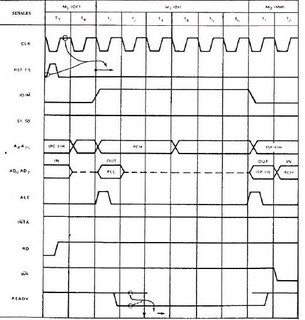

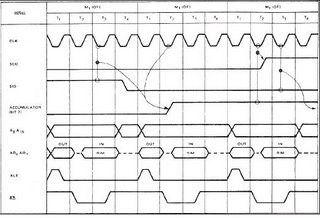

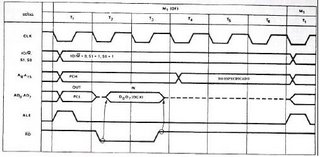

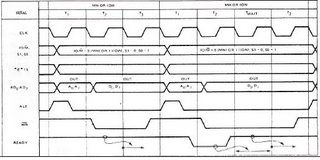

La figura 7-12 muestra la relación de temporización para un ciclo de máquina OF. La

instrucción particular ilustrada es DCX, cuya temporización de OF difiere de las otras instrucciones en que esta tiene seis estados T, mientras que algunas instrucciones solo requieren cuatro estados T para la OF. En este análisis, como en los siguientes, solo veremos la temporización relativa de las señales; para las presentes temporizaciones referirse al Manual de Usuario de la Familia MCS-8085.

La primera cosa que el 8085A hace al inicio de cada ciclo de máquina es el de enviar fuera tres señales de estado (IO/⎯M, S1, S0) que definen que tipo de ciclo de máquina tendrá lugar. La señal IO/⎯M identifica el ciclo de máquina como una operación con referencia a memoria o de entrada/salida. La señal de estado S1 identifica si el ciclo es para una operación de LECTURA o ESCRITURA. Las señales de estado S0 y S1, pueden ser utilizadas en conjunto para identificar los ciclos de máquina de LECTURA, ESCRITURA o BÚSQUEDA DE CODIGO DE OPERACIÓN como también el estado de HALT. Refiriéndonos a la figura 7-12, el 8085-A enviará IO/⎯M=0, S1=1, S0=1 al inicio del ciclo de máquina para identificar como una LECTURA desde una posición de memoria para obtener un código de operación; en otras palabras, éste identifica el ciclo de máquina como un ciclo de BÚSQUEDA DE CODIGO DE OPERACIÓN.

Figura 7-12 CICLO DE MAQUINA DE BÚSQUEDA DE CODIGO DE OPERACIÓN(DE LA INSTRUCCIÓN DCX)

El 8085-A también envía la dirección de 16 bits al inicio de cada ciclo de máquina para identificar la posición particular de memoria o puerto de I/O al que el ciclo de máquina se refiere. En el caso de un ciclo de BÚSQUEDA DE CODIGO DE OPERACIÓN, el

contenido del contador de programa es colocado al bus de direcciones. El byte de orden superior (PCH) es colocado en las líneas A8 – A15 , donde permanecerá hasta por lo menos T4. El byte de orden inferior (PCL) es colocado en las líneas AD0 – AD7, cuyos drivers de tres estados son habilitados si aún no se encuentran activados, a diferencia de las líneas de dirección superiores, sin embargo, la información en las líneas inferiores, permanecerán allá, solo por un ciclo de reloj, después de lo cual, los drivers pasarán a su estado de alta impedancia, indicado por la línea punteada en la figura 7-12. Esto es necesario porque las líneas AD0 – AD7 están multiplexadas en tiempo entre los buses de dirección y datos. Durante T1 de cada ciclo de máquina, AD0 – AD7, saca los 8 bits inferiores de la dirección,

después de lo cual, AD0 – AD7 también sacará los datos designados para la operación de ESCRITURA o se pondrá en alta impedancia (como en el caso del ciclo de OF),

permitiendo que los dispositivos externos manejen las líneas para una operación de

LECTURA.

Como la información de dirección en la líneas AD0 – AD7, son de naturaleza transitoria, deben ser almacenadas ya sea internamente en componentes especiales de bus multiplexado como el 8155 o externamente en las partes como el latch de 8 bits 8212. El 8085-A proporciona una señal de temporización especial denominada ADDRESS LATCH ENABLE (ALE), para facilitar el almacenamiento de A0 – A7; la señal ALE se presenta durante el estado T1 de cada ciclo de máquina.

Después que las señales de estado y dirección han sido enviadas y se han deshabilitado los drivers AD0 – AD7, el 8085-A proporciona un nivel bajo en ⎯R⎯D para habilitar el dispositivo de memoria direccionado. Entonces, el dispositivo comenzará a manejar las líneas AD0 – AD7; ésto está indicado por la línea punteada que se convierte en línea continua en la figura 7-12. Después de un período de tiempo (que es el tiempo de acceso a la memoria) los datos válidos estarán presentes en AD0 – AD7. El 8085-A durante el estado T3 cargará el dato de la memoria en AD0 – AD7 al registro de instrucciones y luego pondrá en nivel alto la señal ⎯R⎯D, deshabilitando el dispositivo de la memoria direccionada. En este punto, el 8085-A habrá finalizado el acceso al código de operación de la instrucción. Como éste es el primer ciclo de máquina (M1) de la instrucción, la CPU pasará automáticamente al

estado T4.

Durante T4, la CPU decodificará en el registro de instrucciones y decidirá si ingresa al estado T5 en el siguiente pulso de reloj o comenzará un nuevo ciclo de máquina y entra al estado T1. En el caso de la instrucción DCX mostrado en la figura 7-12, entrará al estado T5 y luego al T6 antes de ir al T1.

Durante T5 y T6 de DCX, la CPU decrementará el registro designado. Como las líneas A8 – A15 son manejadas por los circuitos de almacenamiento de dirección, que son parte de la lógica de incremento/decremento, las líneas A8 – A15 pueden cambiar durantes los estados T5 y T6 . Como los valores de A8 – A15 pueden cambiar durante T4 - T6, es más importante que todos los dispositivos de memoria y de I/O en el bus del sistema cualifiquen su selección con ⎯R⎯D. Si no utilizan ⎯R⎯D, serán seleccionados de manera espuria. Más aún, con una técnica de selección lineal (ver la Lección 9), dos o más dispositivos pueden ser habilitados simultáneamente, lo cual puede ser potencialmente dañino. La generación de direcciones espurias puede también ocurrir momentáneamente en los períodos transicionales del bus de direcciones en T1. Por lo tanto, la selección de todos los dispositivos de memoria

y de I/O deben ser cualificados con ⎯R⎯D o ⎯W⎯R. Muchos nuevos dispositivos de

memoria como los 8155 y 8355 tienen la entrada de RD que se utilizan internamente para habilitar las salidas al bus de datos, evitando la necesidad de cualificar externamente la entrada de habilitación de dispositivo con ⎯R⎯D.

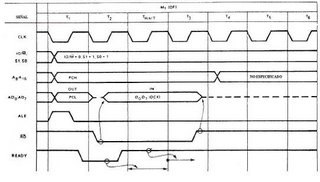

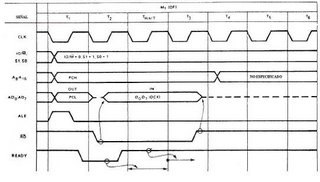

Figura 7-13 CICLO DE MAQUINA DE BÚSQUEDA DE CODIGO DE OPERACIÓN

CON UN ESTADO DE ESPERA

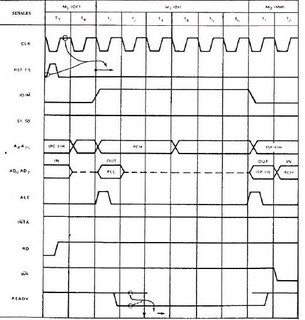

La figura 7-13 es idéntica a la figura 7-12 con una excepción, que es el uso de la línea READY. Como podemos ver en la figura 7-10, cuando la CPU se encuentra en el estado T2,examina el estado de la línea READY. Si la línea READY esta en nivel alto, la CPU procederá con el estado T3 y finalizará la ejecución de la instrucción. Si la línea READY esta en nivel bajo, sin embargo, la CPU ingresará al estado TWAIT y permanecerá en el indefinidamente hasta que la señal READY pase a nivel alto. Cuando la señal READY pasa anivel alto, la CPU saldrá del estado TWAIT e ingresará al estado T3, a fin de completar el ciclo de máquina. Como se muestra en la figura 7-13, el efecto externo de utilizar la línea READY es de preservar el estado exacto de las señales del procesador al final del estado T2 para un número entero de períodos de reloj, antes de finalizar el ciclo de máquina. Este estrechamiento del sistema de temporización tiene el efecto posterior de incrementar el tiempo permisible de acceso para los dispositivos de memoria o de I/O. Mediante la inserción de estados TWAIT, el 8085-A puede acomodar aún las memorias más lentas. Otro uso común de la línea READY es para hacer correr el procesador paso a paso con un interruptor manual.

Temporización del Ciclo de Lectura

LECTURA DE MEMORIA (MR):

La figura 7-14 muestra la temporizavción de dos ciclos de máquina sucesivos de LECTURA DE MEMORIA (MR), el primero sin el estado TWAIT y el segundo con un estado TWAIT. La temporización durante T1 – T3 es absolutamente idéntico al ciclo de máquina de BÚSQUEDA DE CODIGO DE OPERACIÓN, con la excepción de que el estado enviado

durante el estado T1 esa IO/⎯M=0, S1=1, S0=0, identificando el ciclo como de LECTURA

desde una posición de memoria. Esto difiere de la figura 7-12 solo en que S0=1 para un ciclo OF, identificando a dicho ciclo como una operación de BÚSQUEDA DE CODIGO DE

OPERACIÓN. Por otro lado, los dos ciclos son idénticos durante T1 – T3.

Una segunda diferencia ocurre al final del estado T3. Como se muestra en la figura 7-10, la CPU siempre va a T4 desde el estado T3 durante el ciclo M1 que siempre es un ciclo de máquina OF. Durante todos los demás ciclos de máquina, la CPU irá siempre de T3 a T1 del siguiente ciclo de máquina.

Figura 7-14 CICLOS DE MAQUINA DE LECTURA DE MEMORIA (O I/O) CON Y

SIN ESTADOS DE ESPERA

La dirección de memoria usada en el ciclo OF es siempre el contenido del contador de

programa, el cual apunta a la instrucción actual, mientras que la dirección utilizada en el ciclo MR puede tener muchos orígenes posibles. También, los datos leídos durante el ciclo MR son colocados en el registro apropiado, y no en el registro de instrucciones.

LECTURA DE I/O (IOR):

La figura 7-14 también muestra la temporización de dos ciclos de máquina sucesivos de

LECTURA DE I/O (IOR), el primero sin el estado TWAIT. Como aparentemente listo, la

temporización de un ciclo IOR es idéntico a la temporización de un ciclo MR, con la

excepción de IO/⎯M=0 para MR e IO/⎯M=1 para IOR; recuerde que la señal de estado

IO/⎯M identifica la dirección del ciclo de máquina actual seleccionando ya sea una posición de memoria o un puerto de I/O. La dirección utilizada en el ciclo IOR viene del segundo byte (No. de puerto) de una instrucción INPUT. Note que la dirección del puerto de I/O está duplicada en las líneas AD0 –AD7 y A8 – A15. El ciclo IOR solo puede ocurrir como tercer ciclo de máquina de una instrucción INPUT.

Note que la señal READY puede ser usada para generar estados TWAIT para dispositivos de I/O como para dispositivos de memoria. Habilitando la señal READY con las líneas de estado apropiadas, uno puede generar estado TWAIT solo para dispositivos de memoria o solo para dispositivos I/O. Habilitando las líneas de dirección, uno puede cualificar la generación de más estados TWAIT para los dispositivos particulares que están siendo accesados.

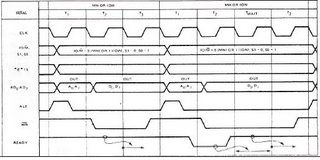

Figura 7-15 CICLOS DE MAQUINA DE ESCRITURA DE MEMORIA (O ESCRITURA DE I/O) CON Y SIN ESTADOS DE ESPERA

Temporización de ciclos de ESCRITURA

ESCRITURA DE MEMORIA(MW):

La figura 7-15 muestra, la temporización de un ciclo de máquina para un I/O WRITE

(IOW) que es el mismo ciclo de máquina MW excepto que la señal IO/⎯M=0 durante el

ciclo MW e IO/⎯M=1 durante el ciclo de IOW.

Como con el ciclo IOR visto anteriormente, la dirección utilizada en un ciclo IOW es el número del puerto I/O, el que se duplica en los bytes superior e inferior del bus de direcciones. En el caso del IOW, el número de puerto proviene del segundo byte de la instrucción OUTPUT cuando se ejecuta la instrucción.

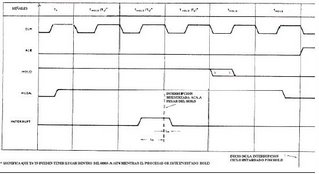

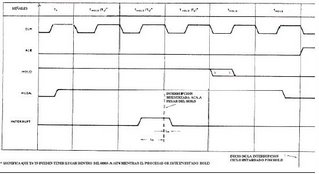

Temporización del Reconocimiento de Interrupción (INA)

Las figuras 7-16 y 7-17 delinean el curso de acción que toma la CPU en respuesta a un nivel alto sobre la línea INTR si el flip – flop INTE FF (flip – flop de habilitación de interrupción ha sido puesto en 1 por la instrucción IE. El estado de los pines TRAP y RST como también INTR son muestreados durante el segundo ciclo de reloj después de M1.T1. Si INTR fue la única interrupción válida y si se ha puesto en 1 el INTE FF, entonces la CPU borrará el INTE FF y luego ingresará al ciclo de máquina INTERRUPT ACKNOWLEDGE (INA). El ciclo INA es idéntico al ciclo OF con dos excepciones. Se envía la señal ⎯I⎯N⎯T⎯A en lugar de ⎯R⎯D. También, la señal IO/⎯M=1 durante INA, mientras que IO/⎯M=0 para OF. Aunque el contenido del contador de programa es enviado a las líneas de dirección, las líneas de dirección pueden ignorarse.

Cuando se envía ⎯I⎯N⎯T⎯A, la lógica externa de interrupciones debe proporcionar el código de operación de la instrucción a ejecutar. El código de operación es colocado en el bus de datos y leído por el procesador. Si el código de operación es el primer byte de la instrucción de múltiples bytes, pulsos adicionales ⎯I⎯N⎯T⎯A serán proporcionados por el 8085-A para temporizar los bytes restantes. Las instrucciones RESTART y CALL son las selecciones más lógicas, ya que ambas fuerzan al procesador a colocar los contenidos del contador de programa en el stack antes de saltar a la nueva ubicación. En la figura 7-16 se asume que el código de operación de CALL es enviado a la CPU durante M1. El código de operación de CALL pudo haber sido colocado por un dispositivo como el controlador de interrupciones programable 8259.

Figura 7-16 CICLOS DE MAQUINA DE RECONOCIMIENTO DE INTERRUPCION (CON LA INSTRUCCIÓN CALL EN RESPUESTA A INTR)

Figura 7-17 CICLOS DE MAQUINA DE RECONOCIMIENTO DE INTERRUPCION (CON LA INSTRUCCIÓN CALL EN RESPUESTA A INTR

Después de recibir el código de operación, el procesador lo decodifica y determina, en este caso, que la instrucción CALL requiere de dos bytes adicionales. Entonces la CPU realiza un segundo ciclo INA (M2) para acceder al segundo byte de la instrucción desde el 8259. La temporización de este ciclo es idéntica a M1, excepto que solo tiene tres estados T. M2 es seguido por otro ciclo INA (M3) para acceder al tercer byte de la instrucción CALL desde el 8259.

Ahora que la CPU ha accesado toda la instrucción utilizada para reconocer la interrupción, ejecutará dicha instrucción. Note que pudo utilizarse cualquier instrucción (excepto EI o DI, las instrucciones que habilitan o deshabilitan las interrupciones). Pero las instrucciones RESTART y CALL son las selecciones más lógicas. Note también que la CPU inhibe el incremento del contador de programa (PC) durante los tres ciclos INA, tal que el valor correcto del PC pueda ser introducido al stack durante M4 y M5.

Durante M4 y M5, la CPU realiza ciclos de máquina de ESCRITURA DE MEMORIA para

escribir los bytes superior e inferior del PC en el tope del stack. Entonces, la CPU pone los dos bytes accesados en la memoria M2 y M3 en los bytes inferior y superior del PC. Esto tiene el efecto de saltar la ejecución del programa a la posición especificada por la instrucción CALL.

Estados del bus inactivo (Bus Idle BI) y en repozo HALT

La mayoría de los ciclos de máquina del 8085-A están asociados ya sea con una operación de LECTURA o ESCRITURA. Hay dos excepciones a ésta regla. La primera excepción tiene lugar durante M2 y M3 de la instrucción DAD. El 8085-A requiere seis estados internos T para ejecutar la instrucción DAD, pero no es deseable que M1 tenga diez (cuatro normales y seis extras) estados de longitud. Por lo tanto la CPU genera dos ciclos de máquina extras que no accesan ni a la memoria ni al I/O. Estos ciclos se refieren como ciclos de máquina inactivos BUS IDLE (BI). En el caso de la instrucción DAD, son idénticos a los ciclos MR excepto que RD permanece en nivel alto y no se genera la señal ALE. Note que la señal READY es ignorada durante M2 y M3 de la instrucción DAD.

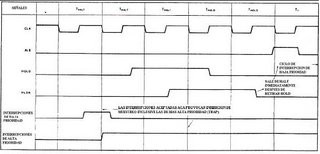

El otro momento cuando ocurre el ciclo de máquina BUS INACTIVO (BUS IDLE) ocurre

durante la generación interna del código de operación RST o TRAP. La figura 7-18 ilustra el ciclo BI generado en respuesta a RST 7.5. Como esta interrupción es de disparo por flanco ascendente, pone a 1 un latch interno; ese latch es muestreado durante el flanco descendente del siguiente al último estado T de la instrucción previa. En este punto la CPU debe generar su propia instrucción interna de RESTART la que provocará (en ciclos de máquina subsiguientes) que el procesador ponga el contador de programa en el stack y apuntar a la posición 3CH. Para hacer ésto, ejecuta el ciclo de máquina OF sin emisión de la señal RD, generando en su lugar el código de operación de RESTART. Después de M1, la CPU continua la ejecución normalmente en todos los aspectos excepto que el estado en la línea READY es ignorado durante el ciclo de BI.

La figura 7-19 ilustra el ciclo BI generado en respuesta al RST 7.5 cuando justamente se ha ejecutado una instrucción HALT y la CPU está en el estado THALT, con sus señales flotando. Solo hay dos maneras de que el procesador puede salir completamente del estado THALT, como se muestra en la figura 7-10. La primera es para que ocurra un RESET, lo que forza siempre al 8085-A a TRESET. La segunda manera de salir del THALT permanentemente es que ocurra una interrupción válida, lo que provocará que la CPU deshabilite más interrupciones borrando el flip flop INTE FF, y proceder luego con M1 . T1 de la próxima instrucción. Cuando la entrada HOLD es activada, la CPU saldrá de THALT por la duración de THOLD y luego retorna a THALT.

En la figura 7-19 la línea RST 7.5 es pulsada durante THALT. Como la RST 7.5 es una

interrupción de disparo de flanco ascendente, pondrá a 1 un latch interno que es muestreado durante CLK=”1” de cada estado THALT (como también durante CLK=”1” dos estados T antes de cualquier M1 . T1). El hecho de que la interrupción almacenada estaba en nivel alto (asumiendo que INTE FF = 1 y la máscara del RST 7.5 = 0) forzará a la CPU a salir del estado THALT al final del siguiente período del CLK, y de entrar a M1 . T1

Esto completa nuestro análisis de la temporización de cada uno de los siete tipos de ciclos de máquina.

Figura 7-18 CICLOS DE MAQUINA DE BUS INACTIVO RST 7.5

Figura 7-19 CICLO DE MAQUINA DE ESTADO DE BUS EN REPOZO E INACTIVO RST 7.5 TERMINA EL ESTADO THALT

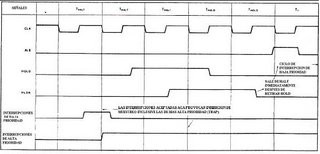

El procesador internamente almacena el estado de la línea HOLD y las interrupciones no enmascaradas durante el CLK=”1” de cualquier estado THALT, la CPU saldra del estado THALT e ingresará al THOLD en el siguiente CLK=”1”. Como se muestra en la figura 7-20 esto ocurrirá aún si ocurre una interrupción válida simultáneamente con la señal HOLD.

El estado del HOLD y de las líneas de interrupción no enmascaradas son almacenadas

internamente durante CLK=”1” de cada estado THOLD como también durante los estados

THALT. Si la señal HOLD internamente almacenada esta en nivel bajo durante CLK=”1”, la CPU saldrá a THOLD e ingresará a THALT en el siguiente CLK=”1”.

El 8085-A acepta la primera interrupción muestreada habilitada no enmascarada; en

adelante, se inhibe todo el muestreo de interrupciones. Las interrupciones aceptadas deberán ser ejecutadas inevitablemente cuando la CPU sale del estado HOLD, aún a expensas de contener las interrupciones de mayor prioridad (incluyendo TRAP). Ver la figura 7-21.

Cuando la CPU no está en THOLD o THALT, almacena internamente la línea HOLD solo

durante CLK=”1” del último estado antes de T3 (T2 o TWAIT) y durante CLK=”1” del último estado antes de T5 (T4 de los seis estados T de M1). Si la señal HOLD almacenada internamente está en nivel alto durante el próximo CLK=”1”, la CPU entrará a THOLD después del siguiente reloj. Cuando la CPU no está en THOLD o THALT, almacenará internamente el estado de las interrupciones no enmascaradas solo durante CLK=”1” del siguiente al último estado antes de cada M1 . T1.

Figura 7-20 HOLD VS INTERRUPCION – NO HALT

Figura 7-21 8085-A HOLD VS INTERRUPCIONES – MODO HALT

Encendido y ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N

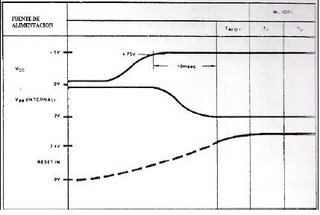

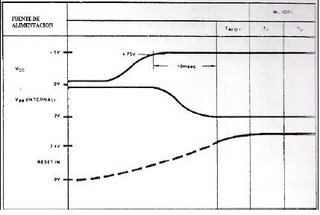

El 8085-A emplea un circuito interno especial para incrementar su velocidad. éste circuito, denominado generador de polarización de sustrato, crea un voltaje negativo utilizado para polarizar negativamente el sustrato. El circuito emplea un oscilador y un fuente de carga que requiere cierta cantidad de tiempo después del ENCENDIDO para estabilizarse. ( Ver figura 7-22).

Tomando en cuenta este circuito, el 8085-A no garantiza trabajar hasta 10 ms después que la Vcc alcanza los 4.75V. Por ésta razón, se sugiere que la señal ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N se mantenga en nivel bajo durante dicho período. Note que los 10 ms no incluyen el tiempo que le toma a la propia alimentación alcanzar el nivel de 4.75V, que podrían ser del orden de los milisegundos en algunos sistemas. Una simple red RC puede satisfacer este requerimiento.

La línea ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N es almacenada cada CLK=1. Esta señal almacenada es

reconocida por la CPU durante CLK=1 del siguiente estado T. (Ver la figura 7-23). Si está en nivel bajo, la CPU emitirá la señal RESET OUT e ingresará al estado THALT para el siguiente estado T. ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N deberá mantenerse en nivel bajo por un mínimo de tres períodos de reloj para asegurar la apropiada sincronización de la CPU. Cuando la señal ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N pasa nivel alto, la CPU entrará a M1.T1 para el siguiente estado T. Note que varias señales y buses están flotantes en TRESET como también en THALT y THOLD. Por ésta razón, es preferible proveer de resistencias de anclaje para las líneas de control principales (particularmente ⎯W⎯R).

Específicamente, la señal ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N causa las siguientes acciones:

BORRA PONE A 1

CONTADOR DE PROGRAMA MASCARA DEL RST 5.5

REGISTRO DE INSTRUCCIONES MASCARA DEL RST 6.5

INTE FF MASCARA DEL RST 7.5

FF RST 5.5

FF TRAP

FF SOD

FF,s DE LOS ESTADOS DE MAQUINA

FF,s DE LOS CICLOS DE MAQUINA

FF,s ALMACENADOS INTERNAMENTE para HOLD, INTR, y READY.

Figura 7-22 TEMPORIZACION DEL ENCENDIDO DE LA FUENTE DE ALIMENTACIÓN

Figura 7-23 TERMPORIZACION DE ⎯R⎯E⎯S⎯E⎯T ⎯I⎯N

La señal R⎯E⎯S⎯E⎯T ⎯I⎯N no cambia explícitamente los contenidos de los registros

(A,B,C,D,E,H,L) del 8085-A y los indicadores de condición, pero debido a la ocurrencia del R⎯E⎯S⎯E⎯T ⎯I⎯N en un momento aleatorio durante la ejecución de la instrucción, el resultado es indeterminado.

Continuando, la señal de RESET, inicializará la ejecución de instrucciones del 8085-A en la posición 0 con el sistema de interrupciones deshabilitado, como se muestra en la figura 7-23.

La figura 7-23 también muestra las operaciones de LECTURA y ESCRITURA siendo

terminadas por la señal RESET. Note que la señal RESET puede terminar prematuramente

cualquier operación de LECTURA o ESCRITURA en proceso cuando ocurre el RESET.

Figura 7-24 RELACION DE LAS SEÑALES SID Y SOD CON LAS INSTRUCCIONES RIM Y SIM

Señales SID y SOD

La figura 7-24 muestra la relación de temporización delas señales SID y SOD con las

instrucciones RIM y SIM. El 8085-A tiene la habilidad de leer la línea SID en el bit 7 del acumulador utilizando la instrucción RIM. El estado de la línea SID es almacenado internamente durante T3CLK=0 de la instrucción RIM. A continuación, el estado de los pines de interrupción y máscara se transfieren directamente al acumulador.

El 8085-A puede ajustar el flip flop SOD desde el bit 7 del acumulador utilizando la

instrucción SIM. Ver la figura 7-25. El dato es transferido desde el bit 7 del acumulador a SOD durante M1.T2.CLK=0 de la instrucción siguiente a SIM, asumiendo que el bit 6 del acumulador esta en 1. El bit 6 del acumulador es el bit de “habilitación de salida serial”.

Figura 7-25 EFECTO DE LAS INSTRUCCIONES RIM Y SIM

LECCION 9

PROGRAMA MONITOR

El programa Monitor reside en las posiciones de memoria ROM 0000 a 0003 y 0040 a

012D. También son utilizadas las posiciones 80DC a la 80FF de la RAM. Si el

interruptor RESET esta en nivel bajo, el MM-8000 comienza a correr el programa

Monitor siempre que la alimentación este encendida. Con el programa Monitor

corriendo, el teclado (que se verá en la lección 12) es usado para introducir datos o

nuevos programas a la memoria. Cualquier byte en la memoria también puede ser

enviado al display. Utilizando el pulsador GO, el control puede ser transferido desde el Monitor a otros programas

El programa monitor opera controlando los parámetros mostrados en la Tabla 9 – 1.

Hay tres modos de operación, Datos (DA), Dirección Baja (AL), y Dirección Alta (AH).

El modo activo esta determinado por el código en el byte Modo L. Como se muestra en

la Tabla 9 – 2, el byte Modo L es puesto en el byte de orden inferior de la dirección del DDA (FC) para el modo DA, DAL (FD) para el modo AL, y DAH (FE) para el modo AH. El byte Modo H siempre contiene 80 que es el byte de orden superior de la

dirección del DDA, DAL y DAH. El modo es puesto presionando los botones correspondientes del teclado. Cada modo opera como sigue.

MODO DATO

En el modo DA los bytes Modo H y Modo L contienen la dirección del byte DDA

80FC. Los dos dígitos hexadecimales de DDA son mostrados en los Displays 1 y 2. No

se iluminan los puntos decimales indicando que el byte DDA esta siendo desplegado.

Cuando una de las teclas de datos del teclado (0 a F) es presionada, los datos son

introducidos en el dígito de orden inferior del DDA y se despliega en el Display 2. El dígito que se encontraba en la posición de orden inferior es desplazado a la posición de orden superior y desplegado en el Display 1.

MODO DE DIRECCIÓN DE ORDEN INFERIOR

En el modo AL los bytes de modo H y modo L contienen la dirección del byte DAL

80FD. Los datos del teclado ahora se introducen en DAL de la misma forma que en

DDA. El despliegue es el mismo excepto que el punto decimal del Display 2 ilumina

indicando que se está mostrando el byte DAL.

MODO DE DIRECCIÓN DE ORDEN SUPERIOR

En el modo AH los bytes modo H y modo L contienen la dirección del byte DAH 80FE.

La operación en el modo AH corresponde al modo AL excepto que el punto decimal del

Display 1 ilumina indicando que el byte DAH esta siendo mostrado.

Cuando el botón de Almacenar del teclado (ST) es presionado, los datos en el byte

DDA son almacenados en la dirección especificada por DH y DAL. Entonces, la

dirección se incrementa en uno y el Monitor es puesto en modo DA mostrando el byte

de datos justamente almacenado

Cuando se presiona el botón GO del teclado , el control es transferido a la instrucción cuya dirección esta especificada por DAH y DAL.

Los botones X1 y X2 del teclado están reservados para uso futuro. Al momento, si se

presionan los botones X1 y X2 se reinicia el programa Monitor.

UBICACIÓN DE MEMORIA

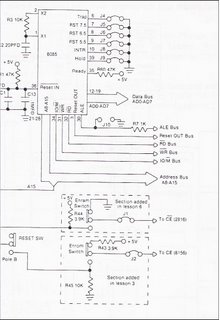

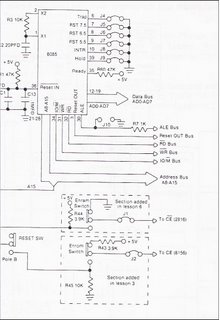

Durante cada ciclo de máquina, el 8085 envía fuera los 16 bits de dirección que nos da 216 = 65.536 posiciones de memoria directamente direccionables. El sistema MM-8000

contiene 2K bytes de memoria ROM y 256 bytes de RAM. Hay por lo tanto muchas

posiciones sin utilizar. Para asignar la ROM y RAM a áreas específicas en el espacio de 64K del campo de memoria, la línea de dirección A15 se utiliza como selector de

dispositivo. A esto se denomina selección lineal. Cuando los interruptores RESET,

ENROM y ENRAM están abajo, la línea de dirección A15 maneja la entrada ⎯C⎯E de

la ROM y la entrada CE de la RAM. Entonces la ROM se selecciona para las

direcciones inferiores a 8.000 y la RAM se selecciona para direcciones superiores a

8.000. Como la RAM solo tiene 256 bytes, solo se necesitan las líneas de dirección A0 a A7. Las líneas A8 a A14 no están decodificadas y pueden estar en 1 ó 0. Por

conveniencia, definiremos con ceros de A8 a A14. La RAM entonces ocupa el espacio

de direcciones de 8000 a 80FF (ver Figura 9 – 1). Similarmente, la ROM ocupa el

espacio de direcciones de 0000 a 07FF.

ENTRADA – SALIDA

El sistema MM-8000 utiliza una entrada/salida mapeada, es decir, que utiliza la línea

IO/⎯M en lugar de una línea de dirección de memoria para distinguir entre los ciclos de I/O y los ciclos de memoria. Durante las instrucciones de entrada salida, el segundo byte (byte de puerto) de la instrucción es enviado por el bus de datos – direcciones y repetido en las líneas de dirección A8 a A15 (ver la Figura 9 – 2). Para habilitar el 8156, el bit 7 del byte de puerto (repetido en A15) debe estar en 1. Como se muestra en las lección 4, el bit 7 no afecta al puerto seleccionado.

EXPANSIÓN

Para proporcionarle al sistema MM-8000 capacidad de expansión de memoria y de I/O

han sido llevadas las líneas necesarias al conector de 44 pines de la tarjeta y a dos conectores de CI de 16 pines.

LECCION 10

PROGRAMA I

El Programa 1 realiza la sección de inicialización del programa Monitor. Las 36

posiciones de memoria ROM, 010ª a 012D, son copiadas a las posiciones de memoria

RAM 80DC a 80FF. Estas posiciones contienen una rutina de retardo de

aproximadamente 10 milisegundos y se la utilizará posteriormente cuando se escriba en

la ROM. Cuando corre ésta rutina en la RAM, solo son accesadas las posiciones de

dirección de la RAM. En la lección 6 se mostró que la escritura en la ROM requiere un

retardo de 10ms. La ROM no puede ser accesada durante éste tiempo de retardo. POr lo

tanto, después de escribir en la ROM , el programa Monitor corre la rutina de 10 ms de retardo en la RAM antes de retornar a la ROM. La sección de inicialización del

programa Monitor también confogura el Puerto A como entrada y los puertos B y C

como puertos de salida. La mayoría de las direcciones de memoria hasta la 0040 están reservadas como posiciones de Trampa y Reinicio. El programa Monitor usa las posiciones 0040 A 005F para tablas de consulta. Como el microprocesador 8085 siempre comienza a correr desde la posición de memoria 0000, en dicha posición una instrucción de salto mueve el programa inmediatamente a la posición 0060 para iniciar la rutina de copia.

El listado de los programas 1 al 4 se puede encontrara en el Apéndice 1. Todos los datos y direcciones en el listado del programa están en hexadecimal a menos que se establezca de otra manera.

DESCRIPCIÓN DEL CIRCUITO

La adición del CI 8085 le permite al microprocesador el control del Bus de Datos AD0 a AD7, y del Bus de Direcciones A8 a A15, y de los Buses de Control que constan de RESET OUT, IO/⎯M,⎯R⎯D,⎯W⎯R, y ALE. Se debe retirar el puente J10 para permitir al 8085 manejar el Bus ALE a través de la resistencia R7. Cuando se repone(RSET) el 8085, la salida ALE se mantiene en nivel bajo permitiendo que el botón ALE controle el Bus como en las lecciones previas. Para evitar entradas no deseadas, los puentes J4 a J9 polarizan las líneas TRAP, RST7.5, RST6.5, RST5.5., INTR y HOLD a tierra, y la resistencia R60 polariza la línea READY a +5V. La resistencia R3 y el capacitor C2 está conectado a las entradas X1 y X2 del 8085 y ponen la frecuencia de reloj a aproximadamente 1.5Mhz.

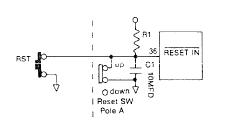

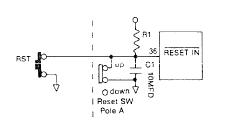

Cuando el interruptor de RESET esta arriba, la entrada ⎯R ⎯E⎯S⎯E⎯T⎯I⎯N del 8085 es

anclado a tierra a través del polo A del interruptor y el 8085 se pone en el estado de reposición. Cuando el interruptor es puesto abajo, se aplica un nivel alto a la entrada ⎯R⎯E⎯S⎯E⎯T⎯I⎯N a través de la resistencia R1 y el 8085 comienza acorrer a partir de la dirección 0000. Si el interruptor RESET esta abajo cuando se enciende el equipo, la aplicación del nivel alto en la entrada de ⎯R ⎯E⎯S⎯E⎯T⎯I⎯N es retardada por los capacitores C1 y C13 para permitir que el sistema se estabilice antes de arrancar el 8085.

Cuando el interruptor RESET está arriba y el 8085 se encuentra en el estado de

reposición, las líneas de dirección, incluyendo la A15, se encuentran en estado de alta impedancia lo que las desconecta efectivamente del Bus de Direcciones. En éste estado los interruptores ENRAM y ENROM operan como se describió en las lecciones 3 y 6.

Antes de bajar el interruptor RESET, los interruptores ENRAM y ENROM deben estar

en la posición abajo (desactivado) para la operación apropiada del sistema MM-8000.

Cuando el interruptor RESET se pone abajo, las líneas de dirección pasan al estado de

baja impedancia. La línea de dirección A15 maneja la entrada ⎯C⎯E del 2816 a través

del interruptor ENROM y el puente J1. La línea de dirección A15 también maneja la

entrada CE del 8156 a través del polo B del interruptor RESET, el interruptor ENRAM,

y J2. Como en las líneas del Bus de Datos las resistencias de anclaje de 3,9K, la

resistencia R44 y la R45 de 10K de anclaje a tierra son sobrepuestas por la baja

impedancia del circuito de la línea A15 en el 8085.

PROCEDIMIENTO

1. Poner el interruptor RESET arriba y todos los demás interruptores abajo.

2. Conectar la fuente de alimentación y encender el equipo.

3. Poner el interruptor ENROM arriba para habilitar la ROM.

4. Poner el interruptor WEN arriba para habilitar la escritura en la ROM.

5. Poner los interruptores de datos a 0000 0000 y presionar el botón ALE para

almacenar esta dirección en el 74HCT573.

6. Poner los interruptores de datos a 1100 0011 (C3 en HEX) y presionar el botón

WR para cargar la primera instrucción del programa en la ROM.

7. Repetir los pasos 5 y 6 cambiando las direcciones y datos para cargar el resto del

programa 1 conforme el listado del Apéndice 1 direcciones 0001, 0002 y 0060 a 0074.

8. Poner el interruptor A8 arriba para acceder a las posiciones d memoria 0100 a

01FF.

9. Repetir los pasos 5 y 6 cambiando las direcciones y datos para cargar el código

de programa listado el Apéndice 1 en las posiciones 010A a 012D. Esta es la

sección del programa Monitor que será usada en el programa posterior.

10. Poner el interruptor WEN abajo para deshabilitar mas escritura a la ROM.

11. Poner el interruptor A8 abajo para retornar a la dirección 0000 a 00FF.

12. Poner los interruptores de datos a 0000 0000 y presionar el botón ALE para

registrar la dirección en el 74HCT573. Pulsar el botón RD para verificar los datos almacenados en esa dirección.

13. Repetir el paso 12 (cambiando la dirección) para verificar que los datos

almacenados en las posiciones 0001, 0002 y 0060 a 0074 están almacenados correctamente.

14. Poner el interruptor A8 arriba para regresar a las direcciones 0100 a 01FF.

15. Repetir el paso 12 (cambiando las direcciones) para verificar que los datos

almacenados en las posiciones 010ª a 012D han sido almacenadsos

correctamente.

16. Poner el interruptor ENROM abajo para deshabilitar la ROM.

17. Poner abajo el interruptor A8 para regresar a las direcciones 0000 a 00FF.

18. Poner abajo el interruptor RESET. El MM-8000 ahora realiza la operación de

copia, pone el Puerto A como entrada y los Puertos B y C como salida y luego

se detiene en la dirección 0074. Como en la lección 4, las salidas de los puertos

son inicializados a cero. Esto hace iluminar todos los segmentos incluyendo el

punto decimal del Display 2.

19. Poner el interruptor RESET arriba para retornar a la operación manual. Note que

la línea de RESET del 8156 retorna los Puetos IO a entradas lo cual hace que se

apague el Display 2.

20. Poner el interruptor ENRAM arriba para habilitar la RAM.

21. Poner los interruptores de datos a 1101 1100 (DC en Hex) y presionar el botón

ALE para registrar la dirección en el 8156. Luego presionar el botón RD para

verificar que el primer byte fue copiado correctamente desde la ROM.

22. Repetir el paso 21 cambiando la dirección desde DD a FF para verificar que los

36 bytes fueron copiados correctamente.

23. Poner el interruptor ENRAM abajo para deshabilitar la RAM.

24. Apagar el equipo.

LECCION 11

PROGRAMA 2

Para el Programa 2 las secciones de despliegue y retardo del Programa Monitor son

adicionados al Programa 1. Para enlazar las secciones de los programas, la instrucción HLT en la posición 0074 del Programa 1 es reemplazada por la instrucción JMP en la posición 0074 en el Programa 2 (ver apéndice 1).

SECCION DE RETARDO

La sección de retardo reside en las posiciones de memoria 80EC a 80F9 de la RAM.

Esta es parte de los 36 bytes copiados de la ROM a la RAM en el Programa 1. El

flujograma de la sección de Retardo se muestra en la Figura 11 – 2. El retardo es

realizado primero cargando el par de registros HL con la constante de retardo.

Seguidamente, se decrementa repetidamente el registro L verificando si llegó a cero (pasos 11A-2 y 11A – 3). Cuando el registro L se hace cero, se decrementa el registro H una vez y luego nuevamente se decrementa el registro L hasta cero. Cuando el registro H alcanza el cero, se completa el retardo.

SECCION DE DESPLIEGUE

La sección de despliegue reside en las posiciones 0077 a 00A4 de la ROM. Las

posiciones 80FA a 80FE de la RAM se utilizan para almacenar los parámetros MODE

L, MODE H, DDA, DAL y DAH. El valor inicial de estos parámetros, mostrados en la

Tabla 11 – 1, son copiados a la RAM desde la ROM al arranque del programa. Como se

mostró en la lección 4, los datos de salida en el Puerto B van a los Displays 1 (display de la izquierda) y Display 2 (display de la derecha). El bit cero del Puerto C controla que Display utiliza los datos. Solo un display está activo por vez. El programa Monitor despliega el dígito de orden inferior, bits 0 a 3 de un byte en el display de la derecha y el dígito de orden superior, bits 4 a 7 en el display de la izquierda. La sección de despliegue del Monitor ingresa el Puerto C y percibe que dígito esta siendo desplegado.

Los datos en el Puerto B son cambiados para desplegar el otro dígito y el bit 0 del

Puerto C se complementa para iluminar el otro display. El Programa 2 retarda entonces y repite la conmutación de despliegue. Si esto se hace lo suficientemente rápido, parecerá como si ambos displays se iluminaran simultáneamente.

Si por ejemplo, el dígito 9 binario 1001 va ha ser desplegado con el punto decimal

iluminado, debe ser sacado al Puerto B el patrón de bits 0011 0000. Para traducir el

1001 a 0011 0000, se utiliza la Tabla Patrón mostrada en el apéndice 1. Los patrones de bits requeridos para desplegar del 0 a F con punto decimal iluminado están almacenados en las posiciones 0040 a 004F. Si como en el ejemplo anterior, se tiene que desplegar un 9 con el punto decimal, el 9 es sumado a la dirección base 0040 para obtener 0049. El patrón de bits contenido en la posición 0049 es sacado entonces al Puerto B.

Si no se requiere el punto decimal, el bit 0 es puesto a 1 antes de sacarlo. Para hacer esto, se genera un byte de punto decimal conteniendo un 1 en el bit 0 para todas las condiciones diferentes al modo AL y Display 2 o modo AH y Display 1. Los bits 1 a 7 son todos ceros (ver la Figura A2-1d del apéndice 2). El byte de punto decimal es mezclado con la tabla patrón antes de sacarlo. Ver la Figura 11 – 3 para el flujograma de la sección de despliegue.

Ver el apéndice 2 para la descripción detallada del Programa 2.

PROCEDIMIENTO

1. Poner el interruptor RESET arriba y todos los demás interruptores abajo.

2. Conectar la fuente de alimentación y encenderla.

3. Poner el interruptor ENROM arriba para habilitar la ROM.

4. Poner el interruptor WEN arriba para permitir la escritura en la ROM.

5. Utilizar el procedimiento habitual (poner los interruptores de datos a la dirección y presionar el botón ALE, luego poner los interruptores de datos al código a ser escrito y presionar el botón WR) para copiar el Programa 2 a la ROM. El

Programa 2 esta listado en el apéndice 1 posiciones 0074 a 00A4.

6. Utilizar el procedimiento habitual para copiar la Tabla Patrón, direcciones 0040

a 004F como se lista en el apéndice 1.

7. Poner el interruptor A8 arriba para acceder a las posiciones de memoria 0100 a

01FF.

8. Utilizar el procedimiento habitual para almacenar FF en la posición de memoria

011C. La dirección de la ROM 011C es copiada a la dirección 80EE de la RAM y llega ha ser el byte de orden superior de la constante de retardo. El valor FF da un retardo de aproximadamente medio segundo.

9. Poner abajo el interruptor WEN para evitar la escritura en la ROM.

10. Utilizar el procedimiento habitual (poner los interruptores de datos con la

dirección para ser verificada y presionar el botón ALE, luego el botón RD para

leer los datos) para verificar el código de programa listado en el apéndice 1 en

las posiciones 010A a 012D. RECUERDE QUE LA POSICIÓN DE MEMORIA 011C HA SIDO CAMBIADA A FF.

11. Poner el interruptor A8 abajo para regresar a las posiciones de memoria 0000 a

00FF.

12. Utilizar el procedimiento habitual para verificar los Programas 1 y 2 en las

posiciones de memoria 0000 a 0002 y 0060 a 00A4.

13. Utilizar el procedimiento habitual para verificar la tabla Patrón almacenada en el paso 6.

14. Poner el interruptor ENROM abajo para deshabilitar la ROM.

15. Poner abajo el interruptor RESET para correr el Programa 2. Como el Programa

está inicializado en el modo data (DA) con la posición de despliegue de datos(DDA) puesta a 00, ambos displays mostrarán ceros sin punto decimal. El Display 1 y Display 2 se alternarán en intérvalos de aproximadamente ½ segundo como se determinó por la constante de retardo en el paso 8. Como en el Programa 1, las salidas de los Puertos son inicializados a cero. Esto hace iluminar todos los segmentos incluido el punto decimal del Display 2, durante el primer período de retardo.

16. Poner el interruptor RESET arriba para detener el programa.

CAMBIO DE LA CONSTANTE DE RETARDO

17. Poner los interruptores ENROM y WEN arriba para habilitar la escritura de la

ROM.

18. Poner el interruptor A8 arriba para acceder alas posiciones 0100 a 01FF.

19. Utilizar el procedimiento habitual para almacenar 05 en la posición de la

dirección 011C. Esta dirección srá copiada en la dirección 80EE de la RAM y

llegará ha ser el byte de orden superior de la constante de retardo. El valor 05 da

un retardo de aproximadamente 10 ms.

20. Poner el interruptor WEN abajo para prevenir la escritura en la ROM.

21. Utilizar el procedimiento habitual para verificar el contenido 05 en la dirección

011C.

22. Poner el interruptor ENROM abajo para deshabilitar la ROM. Como los

interruptores de datos, el interruptor A8 es solapado por el 8085 y se lo puede

dejar arriba.

23. Poner el interruptor RESET abajo para correr el programa. Los displays 1 y 2 se

alternarán en intervalos de aproximadamente 10 ms dando la sensación de que ambos están encendidos continuamente.

24. Poner el interruptor RESET arriba para parar el programa.

PONER EN MODO AL

25. Poner los interruptores ENROM y WEN arriba para habilitar la escritura en la

ROM.

26. Utilizar el procedimiento habitual para almacenar FD en la dirección 0128 y 12

en la 012B. Ver tabla 11-1. La FD de la dirección 0128 es copiada a la dirección

80FA de la RAM poniendo el programa en modo AL. El 12 en la dirección 012B es copiado a DAL en la dirección 80FD de la RAM y será desplegada.

27. Poner el interruptor WEN abajo para prevenir la escritura en la ROM.

28. Utilizar el procedimiento habitual para verificar el FD en la dirección 0128 y 12

en la dirección 012B.

29. Poner el interruptor ENROM abajo para deshabilitar la ROM.

30. Poner el interruptor RESET abajo para correr el programa. El Display mostrará el 12 en el byte DAL. El punto decimal del Display 2 se encenderá indicando que el programa está en modo AL.

31. Poner el interruptor RESET arriba para parar el programa.

PONER EN MODO AH

32. Repetir los pasos 25 al 31. En el paso 26 almacenar FE en la dirección 0128 para

poner el programa en el modo AH. Almacenar 34 en la dirección 012C para que se despliegue. En el paso 30 el diplay mostrará el 34 en el byte DAH y el punto decimal del Display 1 iluminará indicando que el programa está en modo AH. VERIFICACIÓN DE

LA TABLA PATRON

33. Repetir los pasos 25 a 31. En el paso 26 almacenar el número 56, 78, etc. en la

dirección 012C para verificar los bytes restantes de la Tabla Patrón (ver apéndice 1). El punto decimal del Display 1 estará encendido en cada caso indicando que el programa se encuentra en modo AH.

REESTABLECIENDO

34. Repetir los pasos 25 a 31. En el paso 26 reestablecer los bytes de MODEL,

DDA, DAL y DAH a sus valores originales como en la tabla 11-1. En el paso

30, se desplegará 00 sin punto decimal como en el paso 23.

35. Apagar el equipo.

LECCION 12

PROGRAMA 3

El Programa 3 agrega las secciones de Rastreo (posiciones 00A2 a 00D3), Encontrar

Tecla (posiciones 00D4 a 00E1) y Encontrar Datos (Posiciones 00E2 a 00F0) del

programa Monitor al Programa 2. Las secciones de Display y Rastreo estan enlazadas mediante el reemplazo de la instrucción JMP del Programa 2 en las posiciones 00A2 a 00A4 con los 3 primeros bytes de la rutina de Rastreo. Las secciones agregadas permiten que los datos sean introducidos al programa Monitor a través de las 16 teclas de datos. Las 8 teclas de función son rastreadas pero no serán procesadas en el Programa 3. Estas serán adicionadas en el Programa 4.

Cuando se presiona una tecla, es como si se mantuviera presionada durante cientos de

milisegundos. Durante éste tiempo el teclado será rastreado varias veces. El byte de

Habilitación de Procesamiento de Tecla (ENKP) asegura que la tecla será procesada

solo una vez cada vez que sea pulsada. Si la rutina de Rastreo encuentra la tecla

presionada y el byte ENKP puesto (FF), el programa borrará primero el byte ENKP a 00

antes de procesar la tecla y retornará nuevamente a la rutina de retardo. POr el tiempo que el byte ENKP permanezca en cero, se inhibe el procesamiento de otras teclas.. El rastreo continua a intervalos de 10 ms. Cuando la tecla es soltada y la rutina de rastreo se ejecuta sin encontrar una tecla, el byte ENKP es puesto nuevamente a FF para habilitar la siguiente entrada de tecla. El intervalo de 10 ms entre rastreos sirve para antirebote de las teclas.

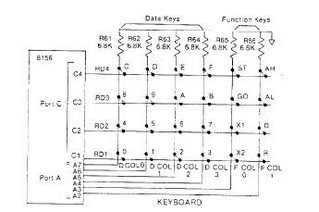

RUTINA DE RASTREO

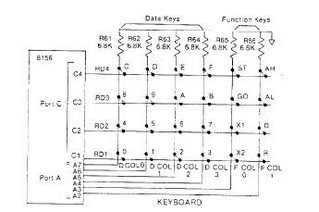

La rutina de rastreo verifica cada una de las 16 teclas de datos y 8 de función para verificar si se encuentran presionadas. Las teclas RST, ALE,WR, RD y RS no son rastreadas. Las 24 teclas rastreadas están ordenadas de manera diferente en el circuito impreso pero se las muestra en la Figura como 4 filas y 6 columnas para ilustrar la naturaleza matricial de la interconexión. Cuando se presiona una tecla, una línea de fila se conecta con la línea de columna. Por ejemplo, si se prsionada la tecla de datos 5, La línea conductor de fila 2 (RD2) se conecta con la Columna de Datos 1 (D COL1). Como se muestra en la figura 12 – 3, el Puerto C está configurado como puerto de salida y maneja las 4 líneas de fila. El Pueto A está configurado como puerto de entrada y rastrea las 6 líneas de columna. En el ejemplo anterior, al presionar la tecla 5 un voltaje alto en la línea RD2 será percibido como un 1

en la línea D COL1. Todas las demás líneas de columna estarán en 0.

El rastreo es iniciado activando RD1. Las líneas de columna son introducidas entonces

al registro A por medio del Puerto A. Estas líneas de columna son rastreadas

secuencialmente desde D COL0 a F COL1. Este ciclo de manejo de filas se repite para RD2, RD3, y RD4. Si una tecla se encuentra presionada, el programa inmediatamente sale de la rutina de rastreo y pasa a la rutina de Tecla Encontrada (KFND). El registro B es usado para almacenar el bit de Fila actual. Inicialmente se pone el bit 1 y luego se saca por el Puerto C para manejar RD1. Conforme se completa cada ciclo de manejo de fila el registro B se desplaza un bit a la izquierda para obtener el siguiente bit de manejo de fila. Cuando el bit se desplaza al quinto lugar concluye el rastreo.

Se usan 5 contadores para controlar el rastreo:

CONTADOR DE DATOS (D CNT): El contador D CNT genera el código hexadecimal

de la tecla de datos presionada. Inicialmente está puesta en 0 y se incrementa cada vez que se prueba la Columna de Datos y que se halla la tecla abierta ( la línea D COL en voltaje bajo). Siempre que se prueba una columna, ya sea de datos o función, y se la encuentra en voltaje bajo, se incrementa el registro E.

Cuando las Columnas de Datos son probadas el D CNT en el registro E y el

Contador de Función (C CNT) en el rgistro L.

Cunando la Columna de Función es probada las posiciones son invertidas. El F CNT en

el registro E y D CNT en el registro L.

CONTADOR DE FUNCION (F CNT): El F CNT indica que tecla de función se ha presionado de manera similar a la D CNT.

Como las teclas de función no están implementadas en el Programa 3, no se las utilizará acá. El Programa 4 implementará las teclas de función.

CONTADOR DE COLUMNA DE DATOS (D COL CNT): El D COL CNT sigue el rastro del número de columnas de dato probadas durante cad ciclo de manejo de filas. Siempre que se prueba una columna, ya sea de datos o función, y se encuentra un voltaje bajo (0), el registro D es decrementado. Este se encuentra en el registro D cuando se rastrea las columnas de datos y en el registro H cuando se rastrea las columnas de función. La D COL CNT s puesta en 04 al inicio de cada ciclo de manejo de fila. Cuando se ha decrementado a cero el rastreo de columna de datos se completa.

CONTADOR DE COLUMNA DE FUNCION (F COL CNT):

CONTADOR DE FUNCION (F CNT): El F CNT indica que tecla de función esta presionada de manera similar al D CNT. Como la las teclas de función no están implementadas en el Programa 3, no será utilizado acá. El Programa 4 implementará las teclas de función.

CONTADOR DE COLUMNA DE DATOS (D COL CNT): La D COL CNT sigue el rastro del número de las Columnas de Datos probadas durante cada ciclo de Manejo de Filas. Siempre que se prueba una columna, ya se de Datos o Función, y se encuentra con voltaje bajo (0), el registro D es decrementado. Como se muestra en la Figura 12 – 5 el D COL CNT esta siempre pareado con D CNT. Este está en el registro D cuando la Columna de Datos es rastreada y en el registro H cuando se rastrea la Columna de Función.. La D COL CNT es puesta a 04 al inicio de cada ciclo de Manejo de Fila.. Cuando ha sido decrementada a cero el rastreo de Columna de Datos ha concluido.

CONTADOR DE COLUMNA DE FUNCION (F COL CNT): La F COL CNT sirve para un propósito similar al de D COL CNT. Este está en el registro D cuando se rastrea un Columna de Función y en el registro H cuando se rastrea una Columna de Datos. Es puesto a 02 al inicio de cada ciclo de manejo de Filas y decrementado por cada prueba

de Columna de Función. Cuando es cero, señala al programa que el rastreo de la

Columna de Función ha concluido.

CONTADOR DATOS/FUNCION (D/F CNT): El D/F CNT reside en el registro C.

Indica que sección de columna de Datos o Función esta siendo rastreada. El D/F CNT

es puesto a 02 al inicio de cada ciclo de Manejo de Fila. Se decrementa a 01 al concluir el rastreo de la columna de Datos y a 00 al completar el rastreo de la Columna de Función. Cuando es cero, la D/F CNT señala al programa que el ciclo de Manejo de Filas se ha completado. La rutina de Tecla Encontrada (KFND) también usa la D/F CNT para determinar si la tecla encontrada fue de datos o de función.

RUTINA DE TECLA ENCONTRADA: La rutina de Tecla Encontrada KFND percibe el estado del byte ENKP. Si el procesamiento de tecla no está habilitado, el control es transferido nuevamente a la rutina de Retardo. Si el procesamiento de tecla está

habilitado, el byte ENKP es borrado para deshabilitar el teclado hasta que se suelte la tecla. Entonces se percibe la señal D/F CNT para determinar si se ha presionado una tecla de datos o función. Si fue presionada una tecla de datos, el control estransferido a la rutina DFND. En el Programa 4 el control será transferido a la rutina F FND si fue precionada una tecla de función. Refiérase a la figura 12 – 6 para el flujograma de la rutina de Tecla Encontrada.

RUTINA DE DATOS ENCONTRADOS: La rutina de Datos Encontrados (D FND) procesa las teclas de datos. El código de la tecla de datos es introducido al byte DDA, DDL o DAH como se especifique por los modos H y Modo L. L dígito de la derecha del byte es desplazado a la posición del dígito de la izquierda y un nuevo código de tecla es

insertado en la posición derecha del dígito.

Ver el apéndice 2 para la descripción detallada del Programa 3.

Con el interruptor de Reposición arriba, el pin ⎯R⎯E⎯S⎯E⎯T⎯I⎯N del 8085 es

puesto a la posición de tierra y el interruptor RST no tiene efecto. Cuando el interruptor Reset esta abajo y el 8085 corriendo, presionando el interruptor RST pone tierra al pin ⎯R⎯E⎯S⎯E⎯T⎯I⎯N y el 8085 se para. Soltando el interruptor RST libera de tierra al pin ⎯R⎯E⎯S⎯E⎯T⎯I⎯N. Esto tiene el mismo efecto que poner el polo A del interruptor RESET abajo como se describió en la lección 10.

Cada tecla se encuentra en la intersección de las líneas de fila y columna. Presionando la tecla conecta la línea de la fila con la de la columna. El Puerto C esta configurado como puerto de salida. Colocando un 1 en el Puerto C, los bits C1 a C4 pone un voltaje alto en la línea de manejo de filas correspondiente RD1 a RD4. Solo una línea de manejo de filas se pone a nivel alto por vez. El Puerto A esta configurado como puerto de entrada. La línea de columna de la Columna de Datos 0 (D COL0) a la Columna de Función 1 (F COL1), son entradas al Puerto A por las líneas A7 a A2. Las líneas de columnas son mantenidas en un voltaje bajo (0) a través de las resistencias R61 a R66. La línea de columna es conducida a nivel de voltaje alto (1) solo cuando un interruptor la conecta a una línea de conducción de Filas activa (nivel alto).

PROCEDIMIENTO

1. Poner el interruptor RESET arriba y todos los demás interruptores abajo.

2. Conectar la Fuente de Alimentación y encender el equipo.

3. Poner el interruptor ENROM arriba para habilitar la ROM.

4. Poner el interruptor WEN arriba para habilitar la escritura en la ROM.

5. Utilizar el procedimiento manual para copiar el Programa · a la ROM. El

Programa 3 esta listado en el apéndice 1 posiciones 00A2 a 00F0.

6. Poner el interruptor WEN abajo para prevenir posteriores escrituras en la ROM.

7. Utilizar el procedimiento habitual para verificar los programas 1,2 y 3 en las

posiciones 0000 a 0002 y 0060 a 00F0.

8. Utilizar el procedimiento habitual para verificar el Patrón de la Tabla en las

posiciones 0040 a 004F.

9. Poner el interruptor A8 arriba para acceder a las posiciones de memoria 0100 a

01FF.

10. Utilizar el procedimiento habitual para verificar las posiciones 010A a 012D.

11. Poner el interruptor EROM abajo para deshabilitar la ROM.

12. Poner abajo el interruptor RESET para correr el programa. Como en la lección

11, el programa inicia en el Modo DDA puesto en 00. El Display por lo tanto

mostrará 00 sin punto decimal.

13. Presionar el botón 1. La pantalla cambia a 01.

14. Presionar el botón 2. El 1 en el dígito de la derecha es desplazado al dígito de la izquierda y el dígito 2 es insertado en el dígito de la derecha.

15. Presionar el botón 3 a F. Note que cada dígito es insertado en el dígito de la

derecha y el dígito anterior es desplazado a la izquierda.

16. Presionar l botón F dos veces para obtener FF en la pantalla.

17. Poner el interruptor RESET arriba y luego abajo. La pantalla mostrará ahora 00.

El FF mostrado en el paso 16 estaba en el byte DDA en la RAM no en la ROM.

El programa es aún inicializado para mostrar 00.

18. Repetir el paso 16.

19. Presionar y soltar el botón RST. Note que tiene el mismo efecto que poniendo el

interruptor RESET arriba y luego abajo nuevamente.

20. Poner arriba el interruptor RESET.

21. Apagar el equipo.

LECCION 13

PROGRAMA 4

El Programa 4 implementa las ocho teclas de función AH, AL, DA, R, ST, GO, X1 y

X2. Para hacer esto, se agrega al Programa 3 la rutina de Encontrar Función (F FND) y

las ocho rutinas de función, Función de Dirección Alta (FAH) hasta la Función X2

(FX2) son adicionadas al Programa 3. Con estas adiciones el programa Monitor está

completo. En el apéndice 3 se muestra el flujograma completo del programa Monitor.

La rutina de Encontrar Función (F FND) (en las ubicaciones 00F1 a 00FF) llevan al

programa Monitor a la dirección de inicio de la rutina de función seleccionada. Las

rutinas de función (en las ubicaciones 0109 y 80DC a 80EB) realizan el trabajo

requerido por la tecla de función particular y luego saltan nuevamente a la rutina de

Retardo.

Rutina Encontrar Función (F FND)

El programa monitor es orientado a la rutina de Función apropiada mediaqnte de la

Tabla de Función mostrada en el apéndice 1. La Tabla de Función contiene la dirección

de inicio de cada rutina de Función. La dirección aparece en la tabla en el mismo orden de rastreo de las teclas asociadas. Para cada dirección se requieren dos bytes. El byte de orden inferior aparece primero seguido inmediatamente por el byte de orden superior. Hay sin embargo dos bytes entre las direcciones.

En la lección 11 se utilizó el código hexadecimal de los datos para acceder a la

dirección apropiada en la Tabla Patrón. De manera similar, el F CNT es utilizado para

acceder a la dirección apropiada en la Tabla de Función. Al inicio de la rutina de

rastreo, la F CNT es inicializada a 28H, (ver la lección 12). Esta es la dirección base (50H) de la Tabla de Función desplazada 1 bit a la derecha. Desplazar un bit a la derecha es equivalente a la división por 2. 50H/2 = 28H. Conforme se rastrea cada tecla de función, la F CNT se incrementa en 1.

Los resultados binarios y hexadecimales del desplazamiento se muestran en las columnas 4 y 5 de la Tabla 13 – 1. Este resultado es el byte de orden inferior requerido de la dirección en la Tabla de Función. La rutina F FND primero

genera la dirección de la Tabla de Función en el par de registros H-L. La dirección de inicio de la Rutina de Función de la Tabla de Función se carga entonces al par de

registros D-E. Para facilitar la ejecución de la rutina de Función los bytes DAH y DAL son puestos en el par de registros H-L y el código MODO L para el modo AH (FE) es

puesto en el registro A. Los pares de registros H-L y D-E son intercambiados y el

control es transferido a la rutina de Función. Cuando el programa entra en las rutinas de Función, los bytes DAH y DAL están en el par de registros D-E.

Rutina de Almacenamiento de Función (FST)

La rutina FST almacena el byte en DDA en la posición de memoria especificada por DAH y DAL. Luego, la dirección en DAH y DAL es incrementada en uno y el programa es colocado en modo DA. Para facilitar la ejecución de las rutinas de FAH, FAL y FDA, el programa es colocado en modo DA poniendo primero en el registro A el código de MODE L para el modo AH (FE). Entonces, se decrementa dos veces el registro A para el modo DA (FC) y se almacena en MODE L.

Rutina de Lectura de Función (FR)

La rutina FR lee el byte de la dirección especificada por DAH y DAL y lo almacena en DDA para desplegarlo. Luego, el control es transferido ala rutina FST para incrementar DAH y DAL y colocar el programa en modo DA.

Rutina de Función FAH, FAL y FDA

La única tarea requerida para las rutinas de Función de Dirección Alta (FAH), Función

de Dirección Baja (FAL) y Función de Dato (FDA) es poner el modo de programa

almacenando el byte apropiado en MODE L. Antes de transferir el control a las rutinas

de Función, la rutina de Encontrar Función pone el código de MODE L para el modo